LibreCar Control Wiki

Welcome to the LibreCar Control Wiki!

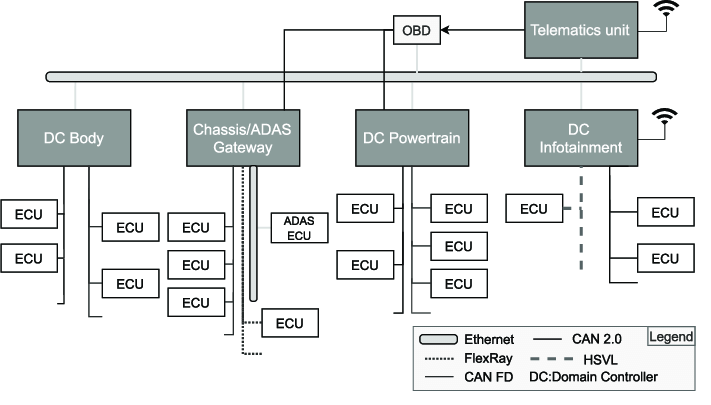

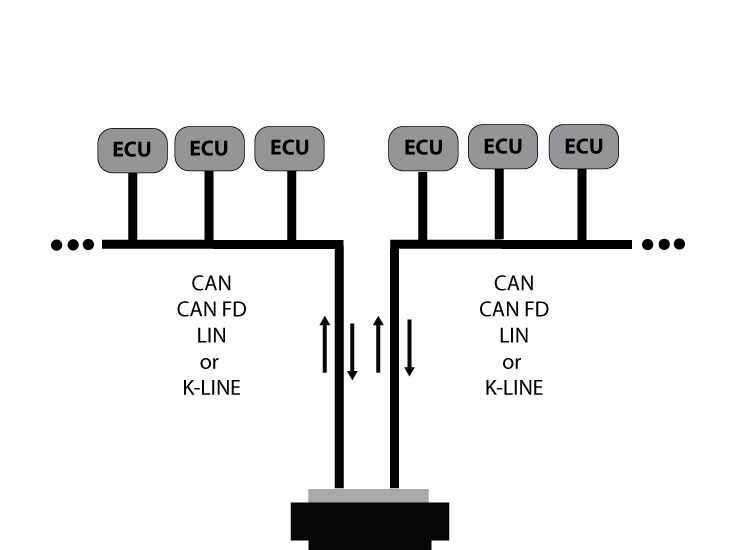

Current trend in automotive world is moving towards a zone architecture that classifies ECUs by their physical location inside the vehicle, leveraging a central gateway to manage communication. This physical proximity reduces cabling between ECUs to save space and reduce vehicle weight, while also improving processor speeds.

ECUs with actuators and sensors are connected by lower bandwidth bus of 1Mb/s with CAN and main connection backbone is higher bandwidth of 10Mb/s or 100Mb/s with Automotive Ethernet.

LibreCar Control is a automotive exploration tool that can emulate connections inside an automotive vehicle talking between different protocols and buses.

It can be used to:

-

Send and Receive CANbus data from any low cost fpga inside a vehicle.

-

Send and Receive Ethernet packets from any low cost fpga inside a vehicle.

- Act as a CAN-Ethernet Gateway allowing the connection of CAN bus over IP networks inside a vehicle.

We use LiteX SoC builder framework to provide a RISC-V soft processor core and integrate with it peripherals like CAN and Ethernet used in automotive world.

Litex Bringup

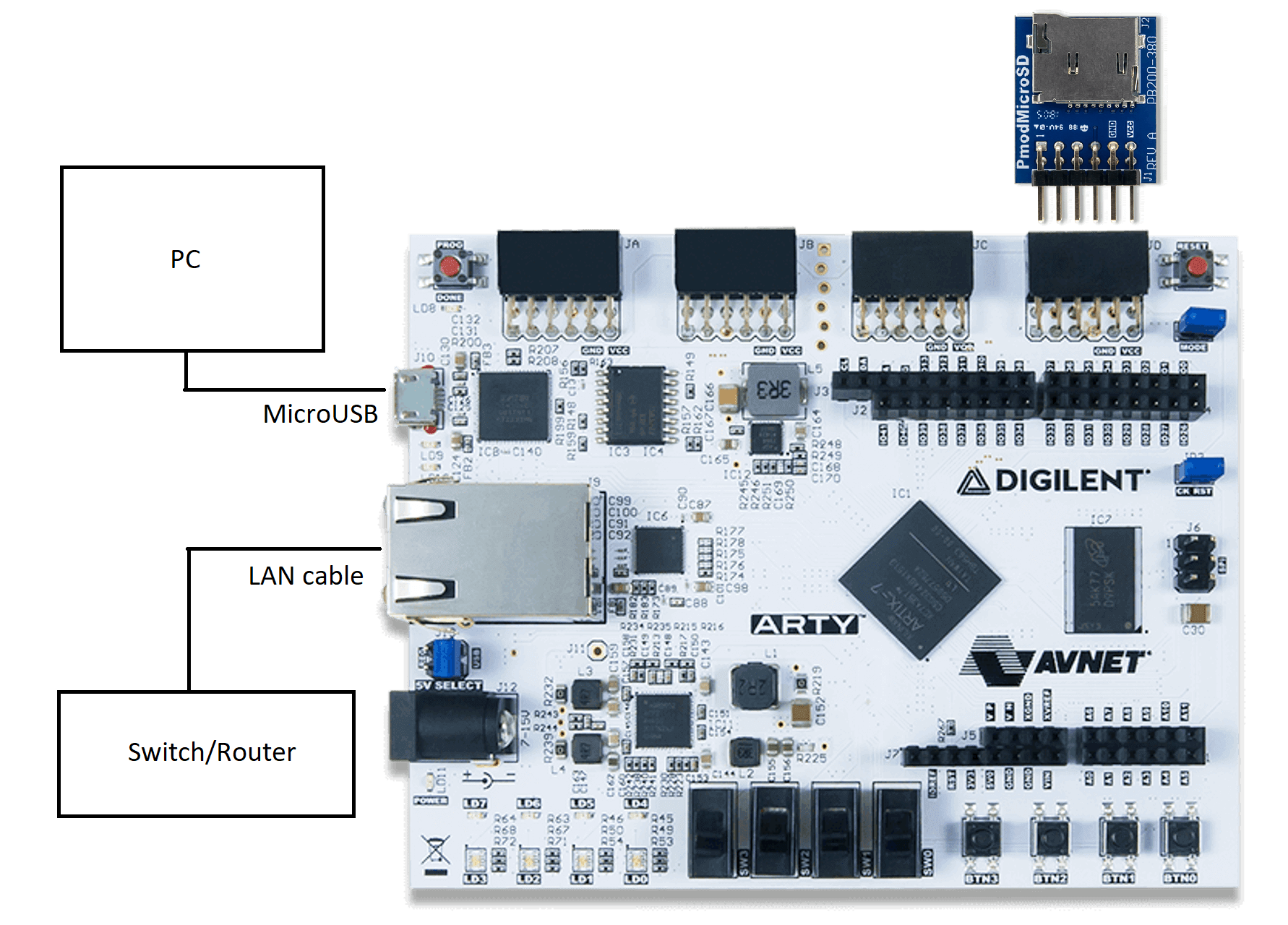

Steps to bringup CAN bus on a 32-bit RISC-V CPU on Xilinx FPGA board Arty A7-100T!

- Install prerequisite packages

sudo apt update

sudo apt upgrade

sudo apt install openocd fakeroot verilator python3 meson gtkterm gawk texinfo git python3-pip bison device-tree-compiler autoconf automake autotools-dev curl python3 libmpc-dev libmpfr-dev libgmp-dev build-essential flex gperf libtool patchutils bc zlib1g-dev libexpat-dev ninja-build

- Checkout Litex Repo.

git clone https://github.com/disdi/litex

cd litex

- Install cross-compiler toolchain for RISC-V.

python3 ./litex_setup.py --gcc=riscv

Install openxc7 or Xilinx Vivado.

- Install Litex pacakges

python3 ./litex_setup.py --dev --init

- Install litex with CAN support

python3 ./litex_setup.py --init --install --user

Apart from all litex packages ctucan_migen_wb_wrapper should also be installed.

- Current CAN Litex support is implemented on Xilinx FPGA board Arty A7-100T.

Checkout Litex Board Repo.

git clone https://github.com/disdi/litex-boards

cd litex-boards

- Build bitstream for Arty board. (Install riscv toolchain and Vivado if not already present.)

python3 litex_boards/targets/digilent_arty.py --variant=a7-100 --build

It creates a bitstream file at build/digilent_arty/gateware/digilent_arty.bit

- Connect Arty A7-100T (J10) to PC using a MicroUSB cable (power, console and programming).

Optionally connect Arty A7-100T (J9) to Switch/Router using a LAN cable and PMOD Sdcard (J10).

Load the bitstream from PC to Arty with –load option or directly using openocd.

python3 litex_boards/targets/digilent_arty.py --variant=a7-100 --load

- Open ttyUSB port to read board serial logs.

To connect to the system’s console, use the screen utility (assuming /dev/ttyUSB1 is used, below):

screen /dev/ttyUSB1 115200

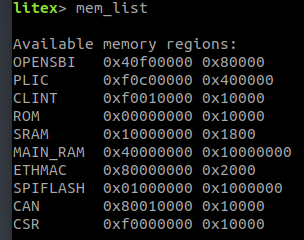

Litex should bootup and mem_list should show CAN peripheral.

This should match the value of CSR register address generated by Litex.

grep "#define CSR[A-Z_]*BASE" build/digilent_arty/software/include/generated/csr.h

Linux Bringup

Steps to bringup Linux on LiteX with a 32-bit RISC-V CPU on Xilinx FPGA board Arty A7-100T and run 32-bit Linux.

- Clone the linux-on-litex-vexriscv reopsitory with CAN support.

git clone https://github.com/disdi/linux-on-litex-vexriscv

- Create bitstream with Linux support for Arty A7-100T and flash it.

./make.py --board=arty --variant=a7-100 --build --load

- Create kernel binaries with CAN support enabled

git clone http://github.com/buildroot/buildroot

cd buildroot

make BR2_EXTERNAL=../linux-on-litex-vexriscv/buildroot/ litex_vexriscv_defconfig

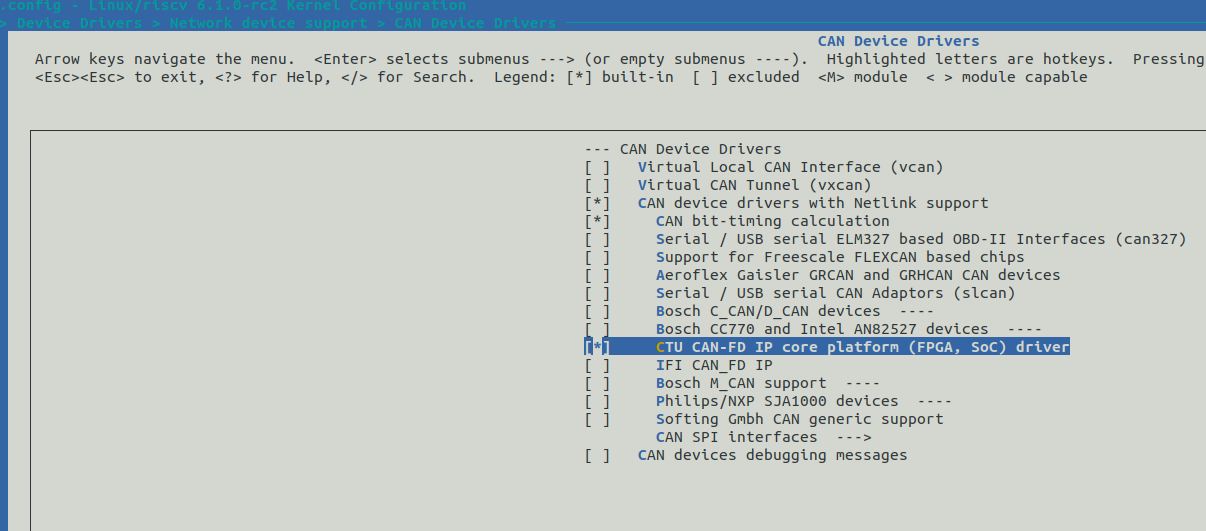

Enable CTUCAN in linux kernel with make menuconfig

Build the kernel binaries

make

The binaries are located in images.

- Create new devicetree since somehow devicetree created by Litex in not currently configurable.

Compile new devicetree binary with dtc compiler and replace it with one created by Litex.

cd patch

dtc -O dtb -o arty.dtb arty.dts

cp arty.dtb images/rv32.dtb

- Load the kernel binaries using TFTP server

Connect the board’s Ethernet port to a switch/router port that places it into the same LAN as the machine acting as your TFTP server.

Ensure that kernel binaries are available in the TFTP directory, and that the TFTP server (or socket, if using systemd) is started:

sudo cp images/* /var/lib/tftpboot/

sudo systemctl start tftp.socket

- Open ttyUSB port to read board serial logs.

To connect to the system’s console, use the screen utility (assuming /dev/ttyUSB1 is used, below):

screen /dev/ttyUSB1 115200

-

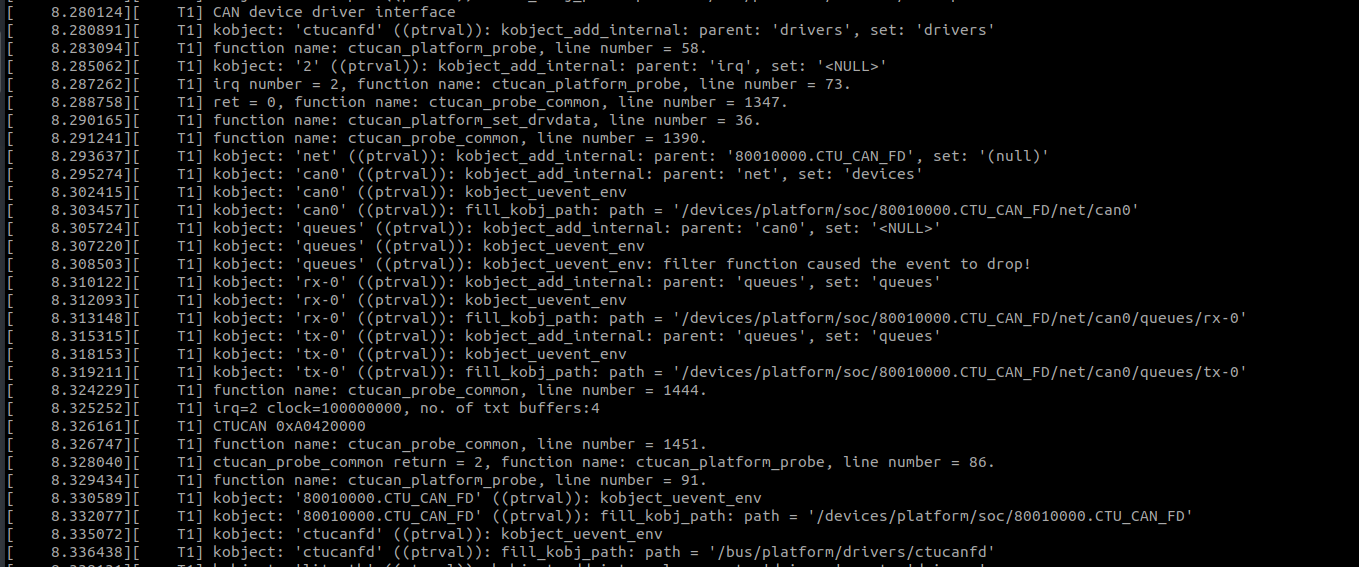

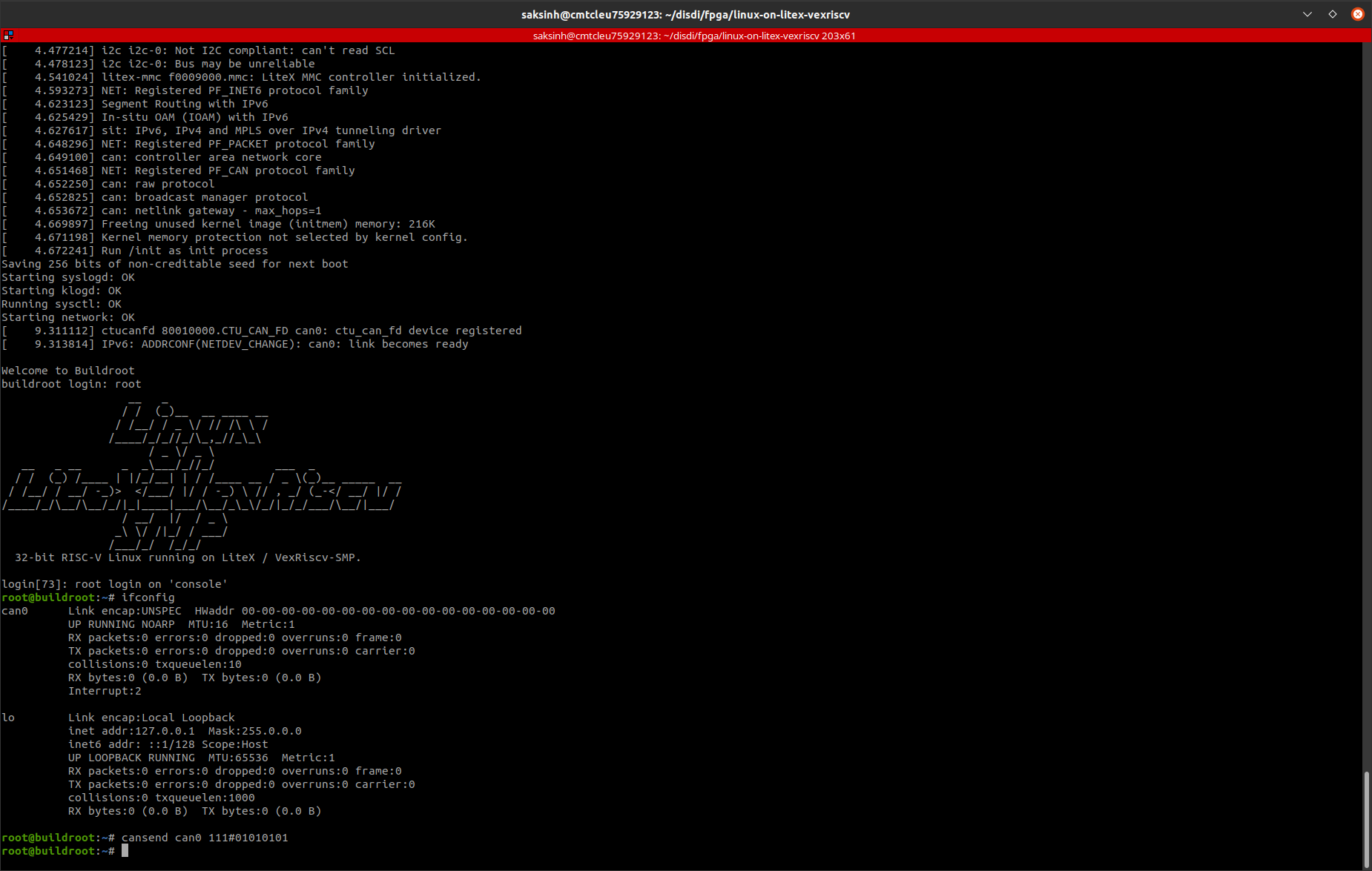

Linux should bootup and bootup logs should show CAN peripheral.

-

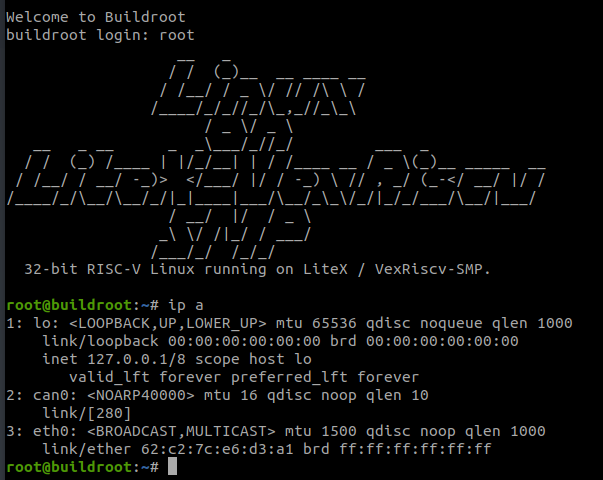

Linux socketcan interface should be up.

Socketcan interface should bringup CAN as a networking device.

Communication with CAN devices

Steps to bringup CAN communication on a 32-bit RISC-V CPU on Xilinx FPGA board Arty A7-100T.

- We would need to install a handful of very useful CANbus utilities for linux. This is packaged as can-utils for Linux.

Enable BR2_PACKAGE_CAN_UTILS=y in buildroot rootfs.

- We would also need iproute2 package to bringup CAN on Linux where it is treated as a network device.

Enable BR2_PACKAGE_IPROUTE2=y in buildroot rootfs.

- Once resulting rootfs is flashed to target, socketcan device can be brought up on Linux with 100 Kbit/s bitrate.

ip link set can0 type can bitrate 100000

ip link set up can0

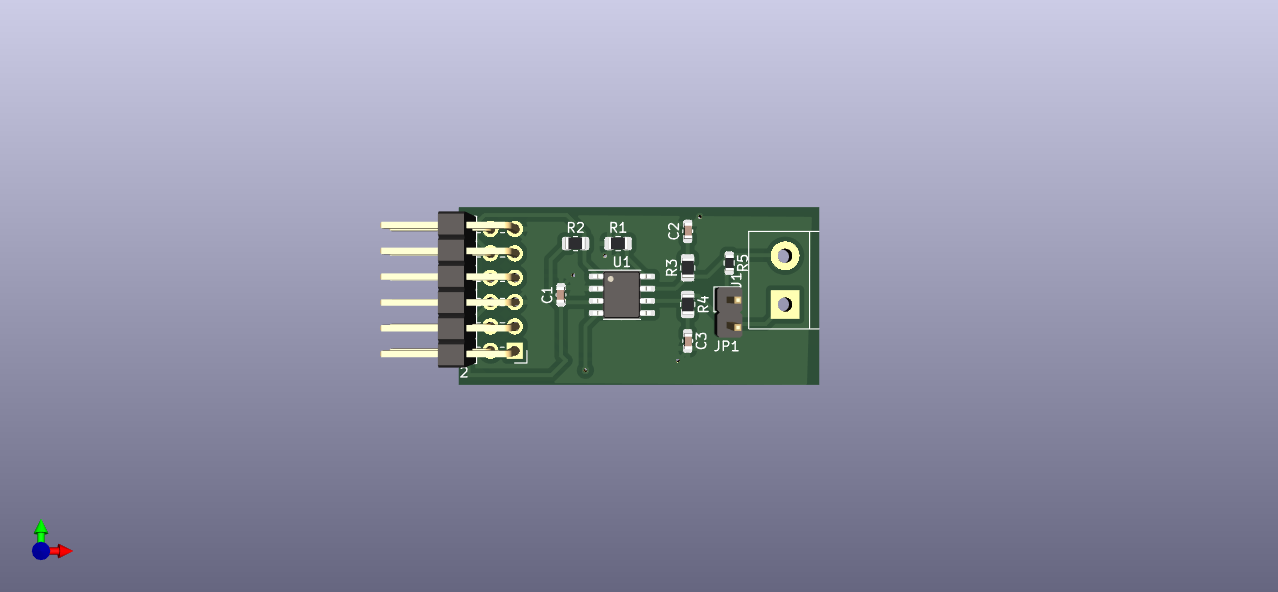

- Connect CAN Controller to CAN Transceiver PMOD

CAN Controller output pins are exposed on PMOD-C(JC) of Arty A7-100T board.

Connect CAN Transciever PMOD designed in this project, for easy connection to fpga board over PMOD-C(JC).

-

Connect a CAN device to other end of CAN Transciever PMOD.

-

Communicate between Arty A7-100T and CAN device usinf cansend from can-utils package.

Funding

This project is funded through the NGI Zero Entrust Fund, a fund established by NLnet with financial support from the European Commission’s Next Generation Internet program.

Learn more on the NLnet project page.